World Journal of Engineering Research and Technology

**WJERT**

www.wjert.org

SJIF Impact Factor: 4.326

# A REVIEW ON DESIGN AND IMPLEMENTATION OF 6T SRAM USING FINFET WITH LOW POWER APPLICATION

Jigyasa Panchal\*1 and Dr. Vishal Ramola<sup>2</sup>

<sup>1</sup>M.Tech Scholar, Dept. of VLSI Design, F.O.T. Uttrakhand Technical University, Dehradun.

<sup>2</sup>Asst. Prof. (H.O.D.), Dept. of VLSI Design, F.O.T. Uttrakhand Technical University,

Dehradun.

Article Received on 05/06/2017 Article Revised on 26/06/2017 Article Accepted on 17/07/2017

\*Corresponding Author Jigyasa panchal M.Tech Scholar, Dept. of VLSI Design, F.O.T. Uttrakhand Technical University, Dehradun.

## ABSTRACT

CMOS devices are facing many problems because the gate starts losing control over the channel. These problems includes increase in leakage currents, increase of on current, increase in manufacturing cost, large variations in parameters, less reliability and yield, short channel effects etc. In the past few years we have come through a new technology

known as FINFET. FINFET is a multi gate device which is used to over come all these problems which are now being faced by CMOS technology especially short channel effects. Since conventional CMOS is used to design SRAM, but it is also facing the problem of high power dissipation and increase in leakage current which affects its performance badly. Memories are required to have short access time, less power dissipation and low leakage current thus FINFET based SRAM cells are recommended over CMOS based SRAM cells. FINFET based SRAM cells are more popular due to the low power dissipation. FINFET based 6T SRAM cell structure differs from the conventional 6T SRAM. Reducing the leakage aspects of the SRAM cells has been very essential to enhance the stability of the cell. Therefore many low power techniques are used to reduce the power dissipation and leakage currents. These include Multithreshold CMOS (MTCMOS), variable threshold CMOS (VTCMOS), Stacking technique, power gating, Self controllable voltage level (SVL) technique etc.

KEYWORDS: CMOS devices are facing many problems.

#### **INTRODUCTION**

The read/write memory is commonly called Random Access Memory (RAM). Read/write (R/W) memory circuits are designed to allow the writing of data bits to be stored in the memory as well their reading on demand. If the stored data can be retained as long as a sufficient power supply is provided then the memory circuit is said to be static. Therefore refresh operation is not required in static RAM. RAMs are classified into dynamic RAM (DRAM) and static RAM (SRAM). SRAM is used to perform three significant operations in a storage management system. These are standby, read, and write operation. SRAM is found better than DRAM in terms of volatility, speed, cost, density, reliability etc. There are certain trade-offs in the design principle of the SRAM. These trade off are between speed and leakage current, read and write stability and between area and yield. There is a requirement that SRAM cell should provide wider noise margin and high speed but it is a major problem because if we require high speed then the leakage power increases. The minimum voltage that a memory cell uses for performing reading operation is called write voltage. A memory cell draws current from the power supply only during switching transition.

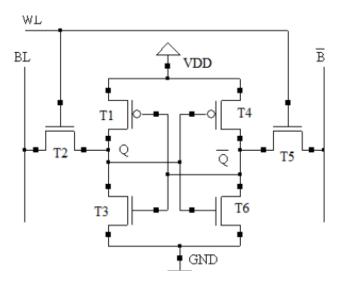

Fig. 1.1: Circuit diagram of SRAM.

## LITERATURE REVIEW

This paper describes low paper FINFET SRAM using multithreshold CMOS technique to reduce the standby power.

[1]"Insights of Performance Enhancement Techniques on FINFET based SRAM cells" Girish and shashikumar:<sup>[1]</sup> This paper discuses the research work focusing on the implementation of SRAM using FINFET. With the advancement in the energy efficient storage system, FINFET has already occupied a place in the area of memory management. This paper also mention about the research gap in the enhancement of the design principle of SRAM designed using FINFET. This paper also makes us aware of the practicality of the research progress.

[2]" A low power single bit line, 6T SRAM cell with high read stability" Budhatiya Majumdar and Sumana Basu:<sup>[2]</sup> Introduces a novel CMOS 6T SRAM cell for different purposes which includes low power application and stand alone SRAM application. The cell proposed consumes less dynamic power and has higher stability. In the proposed technique, the SRAM cell operates on a single bit line during charging and discharging while read and write operation. Due to the proposed technique, the dynamic power consumption is decreased by 40% to 60% as compared to the conventional 6T SRAM CELL. All the simulations are done using multisim on 180µm technology.

[3]"New SRAM cell design for low power and high reliability using 32nm independent gate FINFET technology" Fabrizio Combardi and Yong-bin Kim:<sup>[3]</sup> Introduces a new method for SRAM cell designing in FINFET technology. The proposed design of 8T SRAM cell uses independent gate FINFET in which front and back gates is biased at a different voltage, which can control the current and the threshold voltage. The proposed 8T SRAM cell achieves 48% writing power saving while maintaining the cell performance as compared to the conventional 8T SRAM cell. The proposed 8T SRAM achieve a wide SNM (static noise margin) which is 56% as compared to the conventional 6T SRAM cell. All the simulations are done on the Hspice using ptm model.

[4]" A low power, high speed FINFET based 6T SRAM cell with enhanced write ability and read stability", Yunsik lee and Premvarthi :<sup>[4]</sup> Introduces a FINFET based 6T SRAM cell by combining the advantage of conventional 5T SRAM cell and conventional 8T SRAM cell. The proposed design a tied gate FINFET based 6T SRAM cell with separate read and write path. This proposed design offers low power SRAM with enhanced write ability and is read SNM free. The proposed design uses only one driver transistor and provide better hold SNM and write ability than 5T and 8T SRAM cell. All simulations are done on the predictive technology model at 0.4 vdd. [5]"A high stability, low supply voltage and low stand by power 6T CMOS SRAM", Nobuaki Kobayashi and Ryusuke Ilo: Introduces a new design technique called as self controllable voltage (SVL) to decrease stand by power. The decrease in MOSFET sizes not only increase the leakage current but also results in smaller margin. The proposed design reduces the standby power, increases margin and lower the vdd. This design operates at vdd equal to 0.38v with operating frequency equal to 85 MHz.

[6]"Design of a ternary FINFET SRAM cell", Makani nailesh and satish s. narikhede: Introduces a design of ternary FINFET SRAM cell using multivalued logic(MVL). The design proposes a ternary SRAM using shorted gate FINFET (SG-FINFET) with separate read and write lines. This proposed design show less time delay for read and write operation. The proposed design is implemented in Hspice at 120nm technology and simulations are done with the help of W-Edit version 13.

[7]"Leakage current reduction in FINFET based 6T SRAM cell for minimizing power dissipation in nanoscale memories", Vishal Gupta and Saurabh Khandewal:<sup>[7]</sup> introduces various techniques for reducing the total leakage current for low power SRAM cell. The proposed techniques for reducing the leakage current are multithreshold CMOS (MTCMOS), self controllable voltage level technique (SVL) and proposed DROWSY-CACHE technique. The proposed technique minimizes the total leakage current to 52.89fA and power dissipation to 4.75nw. All simulations are performed on cadence virtuoso 45nm technology.

[8]"Design and Simulation of Low Leakage SRAM CELL", Praveen kumar sahu and Yogesh Mishra:<sup>[20]</sup> Offers a technique to achieve high speed performance and low leakage power for SRAM cell. In this technique, self controllable voltage level (SVL) circuit and dynamic body biasing is applied to the SRAM cell. In the proposed design, the author has proposed three different types of leakage control technique for SRAM cell. Type 1 technique is the combination of body biasing with upper self control voltage technique. Type 2 technique is the combination of body biasing and lower SVL. Type 3 technique is the combination of body biasing and lower SVL. All simulations are done on cadence virtuoso tool using 180nm technology.

[9]"Design of a FinFET Based Inverter Using MTCMOS and SVL Leakage Reduction Technique", Manorma and Saurabh khandewal: Offers design method for FINFET inverter by applying MTCMOS and SVL techniques. These techniques provides high performance and low power dissipation. These techniques uses both low and high threshold sleep transistor. The proposed FINFET based inverter utilizing MTCMOS technique shows 65-70% decrease in leakage power as compared to normal FINFET based inverter. Same goes for proposed inverter utilizing SVL inverter which shows 50-60% decrease in leakage power as compared to normal FINFET based in cadence virtuoso tool at 45nm technology.

[10]"Power and Stability Analysis of a Proposed 12T MTCMOS SRAM Cell for Low Power Devices", Upadhay and Nidhi Agarwal: Offers a proposed 12T MTCMOS SRAM cell which focuses on the power and stability analysis at different range of temperatures. The proposed 12T SRAM cell uses combination of MTCMOS technologies and LVT transmission gate. These LVT transmission gate reduces wake up power and sleep power during transition from sleep mode and active mode during writing operation of the SRAM CELL. The proposed also uses two different voltage sources where one is connected to bitline and other is connected to bitline bar. The combination of MTCMOS and LVT transmission gate reduces the static power. The two different voltage sources used in the proposed design reduces dynamic power dissipation. Thus, the overall power is reduced which provides better stability to the circuit. All the simulation has been done in 45nm CMOS Technology.

[11]"Simulation and Analysis of 6T SRAM Cell using Power Reduction Techniques", Sapna singh and neha arora: Offers aproposed design of 6T sram cell using different power reduction techniques. These low power reduction techniques include stacking technique, asymmetric SRAM cell technique. The comparative analysis of these techniques is done on the basis of different parameters such as power supply voltage, delay, area and operating temperature. The proposed design for 6T SRAM cell shows reduction in the leakage power. All the simulations have been carried on 90nm and 45nm at tanner EDA tool.

[12]"A Novel Power Reduction Technique in 6T SRAM using IGSVL and SGSVL FinFET", G. annalakshmi and S. lakshmi narayana: Offers a proposed design for 6T FINFET SRAM CELL. The proposed design uses shorted gate FINFET and independent gate FINFET. The self controllable voltage level technique is used foe finfet based SG-IG SRAM cell. The proposed design shows reduction in leakage current. All the simulations are carried on tanner EDA tool using 45nm technology.

#### CONCLUSION

The proposed 6T SRAM is designed using FINFET with multithreshold technique (MTCMOS), which uses transistors of different threshold voltage in order to achieve reduce standby power. At last the designed 6T SRAM is implemented on symica tool and simulation results considering dynamic power dissipation are provided. Proper simulation results that justify the operation of each design are given. All circuits are designed in symica software using 14nm technology and also using PTM model.

#### REFRENCES

- G. annalakshmi and S. lakshmi narayanan, "A novel power reduction technique in 6T SRAM using IGSVL and SGSVL FinFET" IISER, May 2014; 5(5): ISSN 2229-5518.

- Christiensen D.C. Arandilla, Anastacia B. Alvarez, and Christian Raymund K. Roque, "Static Noise Margin of 6T SRAM Cell in 90-nm CMOS" 2011 UKSim 13th International Conference on Modelling and Simulation, 978-0-7695-4376-5/11 \$26.00 © 2011 IEEE.

- Vijay Singh Baghel and Shyam Akashe, "Low power Memristor Based 7T SRAM Using MTCMOS Technique"2015 Fifth International Conference on Advanced Computing & Communication Technologies, 2327-0659/15 \$31.00 © 2015 IEEE.

- Leila Bagheriye, Roghayeh Saeidi and Siroos Toofan, "Low Power and Roboust FinFET SRAM cell Using Independent Gate Control" 978-1-4799-5341-7/16/\$31.00 ©2016 IEEE.

- Aditya Bansal, Saibal Mukhopadhyay and Kaushik Roy, "Device-Optimization Technique for Robust and Low-Power FinFET SRAM Design in NanoScale Era" IEEE Transactions on Electron Devices, June 2007; 54(6).

- Girish H. and Shashikumar D. R., "Insights of Performance Enhancement Techniques on FinFET-based SRAM Cells" Communications on Applied Electronics (CAE) – ISSN : 2394-4714 Foundation of Computer Science FCS, New York, USA, 5(6): July 2016.

- T-H Joubert, E Seevinck, M du Plessis, "A four-transistor CMOS SRAM cell" 0-7803-5546-6/99/ 1999 IEEE.

- Vishal Gupta and Saurabh Khandelwal, "leakage current reduction in finfet based 6t sram cell for minimizing power dissipation in nanoscale memories" 2015 5th Nirma University International Conference on Engineering (NUiCONE), 978-1-4799-9991-0/15/ ©2015 IEEE.

- Young Bok Kim, Yong-Bin Kim and Fabrizio Lombardi, "New SRAM Cell Design for Low Power and High Reliability using 32nm Independent Gate FinFET Technology " IEEE International Workshop on Design and Test of Nano Devices, Circuits and Systems, 978-0-7695-3379-7/08 © 2008 IEEE.

- Makani Nailesh Kishor and Satish S. Narkhede, "Design of a Ternary FinFET SRAM Cell" 1st IEEE Symposium on Colossal Data Analysis and Networking (CDAN), 978-1-5090-0669-4/16/\$31.00 © 2016 IEEE.

- M. Bayoumi, A. Dutta, "FinFET based SRAM Design: A Survey on Device, Circuit, and Technology Issues", *IEEE International Conference on Electronics, Circuits and Systems*, 2014; 387-390.

- Nobuaki Kobayashi, Ryusuke Ito and Tadayoshi Enomoto, "A High Stability, Low Supply Voltage and Low Standby Power Six Transistor CMOS SRAM" 978-1-4799-7792-5/15/\$31.00 ©2015 IEEE.

- Budhaditya Majumdar and Sumana Basu, "Low Power Single Bitline 6T SRAM CellWith High Read Stability" 2011 International Conference on Recent Trends in Information Systems, 978-1-4577-0792-6/11/\$26.00 ©2011 IEEE.

- 14. Manorama, S. Khandelwal, and S. Akashe, "Design of a FinFET based Inverter using MTCMOS and SVL Technique reduction Technique," Proceeding of the 2013 Students Conference on Engineering and Systems, April 2013; 1-6.

- 15. Rahaprian mudiarasan premvarthi, Qiand tong, and yunsik lee, "A low power, high speed FinFET based 6T SRAM cell with enhanced write ability and read stability" ISOCC 2016 978-1-5090-3219-8/16/\$31.00 ©2016 IEEE.

- 16. Praveen Kumar Sahu, Sunny, Yogesh Kumar and V. N. Mishra, "Design and Simulation of Low Leakage SRAM CELL" Third International Conference on Devices, Circuits and Systems (ICDCS'16) 2016 IEEE.

- 17. P. Upadhyay, Nidhi Agarwal, R. Kar, D. Mandal, S. P. Ghoshal, "Power and Stability Analysis of a Proposed 12T MTCMOS SRAM Cell for Low Power Devices" 978-1-4799-4910-6/14 \$31.00 © 2014 IEEE, ACCT.2014.18.

- Sachin Chauhan and Sagar Raj, "Leakage Current Minimization in a 6t SRAM Cell" SSRG International Journal of Electronics and Communication Engineering (SSRG-IJECE), May 2016; 3(5):

- 19. Ankita Tiwari and Raghvendra Singh, "Design low power SRAM using MTCMOS Technique with Nanometer Regime" Intl J Engg Sci Adv Research, 2016 Dec; 2(4): 1-4.

- 20. Bhanupriya Bhargava, Pradeep Kumar Sharma, "Comparative Analysis of Self-Controllable Voltage Level (SVL) and PowerGating Leakage Reduction Techniques Using in Sequential Logic Circuitat 45 Nanometer Regime" International Journal of Engineering Research & Technology (IJERT), 2(12): December–2013.

- Subham Sriwastava, Kumar Shubham, "MTCMOS Based 14T SRAM Cell Optimized for High Performance Applications" International Journal of Engineering Research & Technology (IJERT), January-2017; 6(01).

- Sapna Singh, Neha Arora, Neha Gupta, "Simulation and Analysis of 6T SRAM Cell using Power Reduction Techniques" IOSR Journal of Engineering (IOSRJEN), Jan.2012; 2(1): 145-149.

# BIOGRAPHY

Jigyasa panchal received B.Tech degree in Electronics and Communication Engineering from DBITW (Uttarakhand Technical university, Dehradun) in 2013 Presently pursuing M.Tech in VLSI Design from Faculty of Technology, Uttarakhand Technical University, Dehradun.

Dr. Vishal Ramola is currently working as an Assistant Professor (H.O.D.) in VLSI Design Department of F.O.T., Uttarakhand Technical University, Dehradun. He completed his Ph.D. From Uttarakhand Technical University, Dehradun in 2015. He did his M.Tech in VLSI Design From UPTU in 2007 and B.Tech. in Electronics and telecommunication Engineering from Amrawati University in 1998. His current research interest include Circuit Theory and VLSI Physical Design.